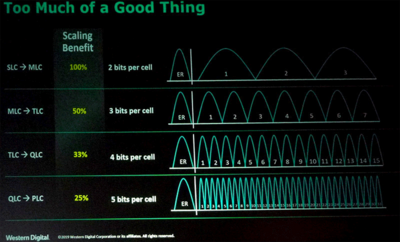

Los fabricantes de memoria NAND 3D, la usada en las unidades de estado sólido y otro tipo de memoria flash, siguen centrados en aumentar la capacidad de los chips a base de apilar más capas de memoria. La otra forma de aumentar la capacidad es aumentando la cantidad de bits que se guardan en cada celda de esta memoria, siendo lo habitual hoy en día que se guarden tres (TLC). Hay algunas soluciones que guardan cuatro (QLC) pero tiene otra serie de problemas que lastran su implantación. Lo que Western Digital tiene claro es que la memoria que almacena cinco bits por celda (PLC) no será viable hasta la segunda mitad de la década.

Esto tiene que ver con el funcionamiento de la memoria NAND. Para representar los bits se guarda en la celda en forma de un voltaje, y según el valor del voltaje será un conjunto de bits u otro. En el caso de la memoria TLC, hay ocho rangos distintos, mientras que en la PLC se llegaría hasta los treintaidós rangos distintos. El problema está en que a medida que se graba en la celda el sustrato se degrada y se va haciendo más probable que el voltaje guardado difiera del voltaje que se pretendía guardar. Además de un sistema más preciso para guardar y leer las celdas se precisa más espacio para circuitos de corrección de errores (ECC) y otros. Eso redunda también en una menor durabilidad de las celdas.

Al final la ganancia de capacidad respecto a la memoria QLC es de un 25 % —se pasa de tener cuatro bits por celda a tener cinco—, que es menor que el 33 % del paso de la TLC a QLC. Las compañías tienen que solucionar primero los problemas de la QLC, que son los mismos que la PLC y cualquier celda de memoria NAND en general. Entre otros, el hecho de que el ECC introduce un procesamiento adicional que requiere de más núcleos —generalmente son Cortex R para microcontroladores— o mayor potencia de ellos, o generaría una pérdida de rendimiento.

Sea como sea, y como dice Western Digital, no parece que la memoria PLC sea viable a nivel comercial hasta dentro de unos años.

Vía: Tom's Hardware.