ARM presentó a principios de febrero las bases de la arquitectura que llegará en los procesadores de dispositivos móviles de 2016. Se trata de los núcleos Cortex-A72 de los procesadores, pero sólo dio detalles sobre los aspectos generales de los mismos. Durante el TechDay 2015 celebrado en Londres ha dado más detalles sobre los mismos.

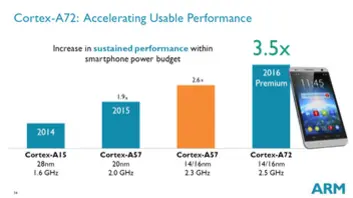

Estos núcleos prometen un 350% de mejora en su rendimiento con respecto a los Cortex-A15 encontrados en procesadores como el Nvidia Tegra 4 o diferentes modelos de Exynos de Samsung. Con respecto a los núcleos Cortex-A57 de procesadores de 64 bits usados este año su potencia es casi del doble.

La arquitectura está basada en un proceso de integración a 14 y 16 nm FinFET, de la que sólo Samsung e Intel por el momento son capaces de producir procesadores con buenos rendimientos de producción. TSMC debería estar ya preparada para producir chips de este tipo, pero la experiencia de Samsung en el sector tiene un gran peso. La frecuencia de funcionamiento de los chips se centraría en los 2,5 GHz.

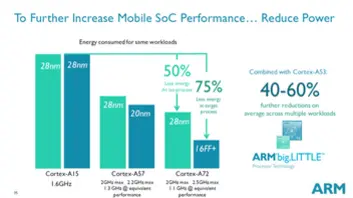

El cambio en proceso de fabricación de los transistores a 14 nm viene acompañada de una reducción de consumo, unido con el tipo de transistores FinFET. Es una reducción de más del 50% de consumo con respecto a los núcleos Cortex-A57 de 64 bits actuales, o del 75% con respecto a los Cortex-A15.

Puesto que la tecnología de las baterías parece que no avanza nada, es más importante que nunca que los procesadores reduzcan su consumo al mínimo. Además que esto permite un objetivo que tiene ARM y es que los núcleos funcionen el mayor tiempo posible a su frecuencia máxima. Normalmente los procesadores móviles tras un corto espacio de tiempo reducen su potencia para evitar calentamiento y/o reducir el consumo.

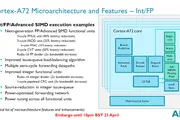

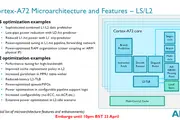

La mejora en rendimiento procede de la nueva microarquitectura que acompañará a estos núcleos. Están resumidos en las siguientes transparencias.

Poseen un mejor predictor de saltos con un nuevo algoritmo que permite reducir consumo y mejorar su efectividad, mejora el ancho de banda entre componentes y más memoria caché L2, mejora la caché L1, mejoras de latencia en la ejecución de instrucciones, y otros cambios en realidad a toda la microarquitectura que permite obtener pequeñas ganancias en cada apartado y que al final se traducen en grandes ganancias.

Vía: AnandTech.