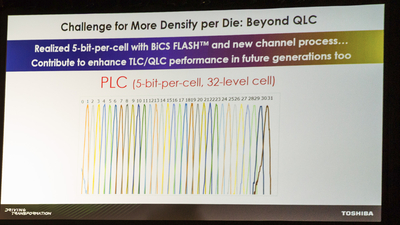

Los fabricantes de memoria NAND se han quedado estancados en aquella que almacena cuatro bits por celda (QLC), pero Toshiba ha empezado a hablar sobre sus avances relacionados con la de cinco bits por celda (PLC). Este tipo de memoria permitiría aumentar aún más la densidad de bits por chips de NAND, pero tiene una serie de problemas aparejados.

El último nivel de división de la memoria NAND son las celdas, las cuales almacenan la información, pero como niveles de tensión. Una memoria NAND de tipo SLC (un bit por celda) solo tiene dos posibles voltajes que serían un cero o un uno. Una de tipo MLC almacena dos bits por celda, que son cuatro valores posibles (00, 01, 10, 11) y cada uno es un voltaje —o más bien rango de voltajes—. La memoria TLC almacena tres bits por celda y ya se pasa a ocho rangos de voltajes posibles. La memoria QLC (cuatro bits por celda) pasa a dieciséis rangos de voltajes, y la PLC pasa a tener treintaidós rangos de voltajes posibles.

El problema de la memoria NAND es que para eliminar el valor anterior guardado en una celda hay que aplicar una tensión de borrado que daña poco a poco la celda. Con el paso del tiempo, los voltajes no se guardan con la misma precisión y puede ocurrir que al querer guardar el voltaje del valor 01 en realidad se almacene el del valor 00. Los controladores de las SSD lo detectan y marcan la celda como inutilizable.

Se puede ver en la imagen superior los valores de la memoria PLC, generalmente guardados entre los 0 y 11 V, que podrían tener en torno a los 300 mV de margen para cada posible valor. Eso lleva a que se necesite una mayor precisión en el guardado y lectura de los voltajes, y Toshiba ha conseguido hacer funcionar esta memoria PLC modificando su memoria QLC actual.

Pero para llevarlo al plano comercial, necesita hacer una serie de cambios a la producción de la memoria que llevará tiempo y potencialmente reducirá la velocidad de esta memoria y su durabilidad. Los controladores actuales no pueden convertir la información al formato QLC a la velocidad adecuada, y para la PLC sería incluso peor. Se están introduciendo en el protocolo NVMe de las SSD de tipo PCIe algunas características adicionales como zonas con nombres de espacio (ZNS) para que las aplicaciones se encarguen de decidir dónde guardan la información y no el controlador, y reducción de otros problemas que ahora mismo requiere un sobreaprovisionamiento en las SSD.

Todo esto está en desarrollo o, más bien, en investigación para ver si es realmente viable y le interesa a la compañía seguir por ese camino. Hay otras formas de aumentar la densidad de bits, como la reducción de la litografía, pero esto también tiene problemas similares en cuanto a la durabilidad —a menor nivel de proceso litográfico menor la durabilidad—.

Vía: Tom's Hardware.