El sector de la producción puntera de chips tiene entre manos varias formas de mejorar su rendimiento y consumo porque ya no sirve solamente con reducir el tamaño de los transistores. No sirve desde hace bastante, pero ahora se precisa aplicar ciertas técnicas de las que se viene hablando a nivel universitario desde hace unos años. Una de ellas es la entrega trasera de energía (backside power delivery) y que Samsung podría usar en una futura revisión de su proceso de 3 nm o dejarla para los 2 nm.

Es una técnica con la que Samsung, Intel y TSMC están experimentando y que introducirán en sus procesos litográficos en distintos momentos. En un documento del simposio VLSI de finales de junio, Samsung indicó que la introducción de esta forma de entregar la energía a los transistores redujo un 14.8 % el área de un procesador, mientras que dos procesadores de arquitectura Arm la reducía en 10.6 % y 19 %. No indicó qué chips eran.

Esa reducción de área significa que la compañía puede jugar con ella para aumentar el número de transistores y aumentar su potencia, que con esta entrega trasera de energía permitiría un aumento de un 10-20 % en los chips indicados manteniendo el mismo área. Pero además, al usar la entrega trasera de energía, hay una reducción en la longitud de las conexiones entre componentes, lo cual permite usar pistas más gruesas con menor resistencia, lo cual mejora la corriente entregada y por tanto mayor rendimiento.

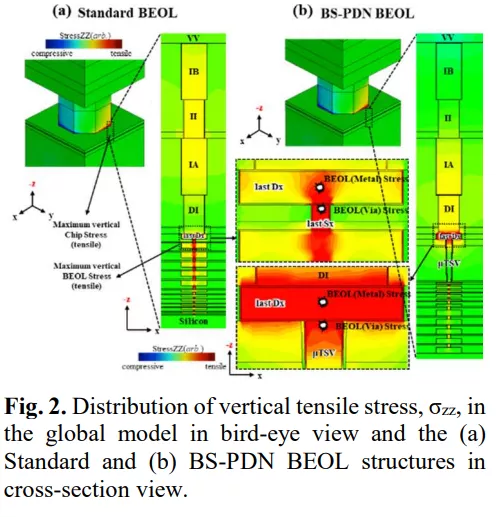

La gestión trasera de energía consiste en mover la entrega de energía a la parte más inferior de la oblea, donde se crean los transistores, en lugar de tener que atravesar capas y capas de la oblea hasta entregarles la energía. Se aumenta la integridad de la señal al reducir el ruido, tiene menores pérdidas y permite una mayor densidad de chips. La desventaja es que aumenta la complejidad de fabricación, tanto por maquinaria a usar como por pasos extras a dar en el proceso de fabricación de las capas.

Vía: Tom's Hardware.