Cuando todavía no ha llegado PCIe 5.0 a los centros de datos y al mundo del PC en general ya se está finalizando la especificación PCIe 6.0. El grupo PCI-SIG dedicado a su desarrollo ha publicado una nueva versión de la especificación, la 0.7, sin cambios sustanciales en lo referente al funcionamiento del estándar. El desarrollo de PCIe 6.0 avanza a grandes pasos debido a la necesidad de los centros de datos al movimiento de grandes cantidades de información entre dispositivos conectados a los procesadores.

PCIe es un protocolo a nivel físico que va a ser utilizado por otros protocolo a nivel de enlace como el CXL que desarrolla Intel y al que se ha sumado a su desarrollo multitud de empresas, incluida AMD, para usar de esta forma un protocolo que no imponga un sobrecoste excesivo en la transferencia de información. Su uso en el ámbito doméstico no tiene mucha utilidad como tampoco la tiene PCIe 5.0. Al menos de momento.

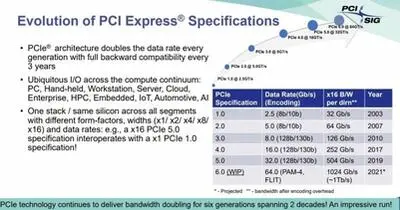

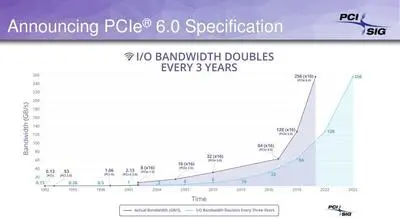

La versión PCIe 6.0 duplica otra vez la velocidad de transferencia, pasando de 32 Gb/s por canal a 64 Gb/s, si bien hay un cambio en la transferencia al usarse un código de línea PAM4 en lugar de un 128b/130b. Esto último significa que cada 128 bits enviados se añaden dos de control y por tanto se envían 130 bits, mientras que PAM4 es un código de línea que os sonará de hace poco ya que es el mismo usado internamente por la GDDR6X, pero no es nada nuevo.

PAM4 envía los bits de dos en dos (dupla) asignando un nivel de voltaje distinto a cada dupla (00, 01, 10, 11) en lugar de pasar de cero a cinco voltios (por poner un ejemplo) dependiendo de si se envía un cero o un uno. Se requiere de un circuito más complejo para realizar el envío y recepción, pero se aumenta la tasa de transferencia real manteniendo casi la misma frecuencia de reloj. En la práctica elimina el sobrecoste de un campo de control en el envío de datos y por tanto 64 Gb enviados son 64 Gb recibidos, y una conexión PCIe 6.0 ×16 podrá alcanzar los 1024 Gb/s máximos que permite este enlace.

Otros cambios adicionales tienen que ver con la mejora de los códigos de corrección de errores, reduciendo su impacto en la eficiencia del ancho de banda y reduciendo la latencia de su aplicación.

La especificación estará lista en 2021 según lo previsto.