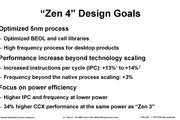

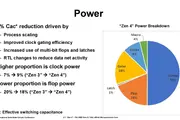

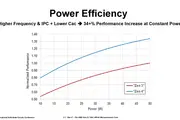

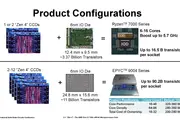

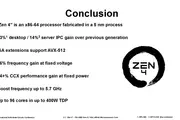

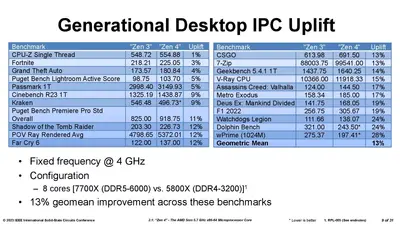

AMD ha participó en la Conferencia Internacional de Circuitos de Estado Sólido (ISSCC) en la que habló bastante más sobre sus últimos procesadores, la arquitectura Zen 4 y el proceso litográfico de 5 nm utilizado para ellos. Eso incluye imágenes y desglose tanto de los chíplets de computación (CCD) como el de E/S (IOD). De entrada la compañía habla de un 34 % más de rendimiento del complejo de núcleos (CCX) de tipo Zen 4 integrado en el CCD frente al Zen 3 usado en la pasada generación a mismo consumo.

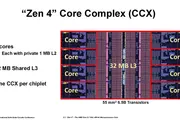

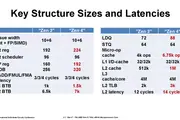

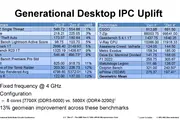

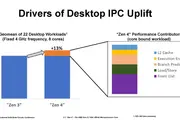

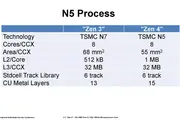

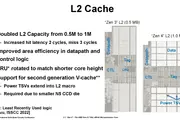

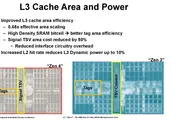

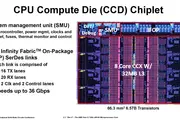

Se ha mostrado que es una buena arquitectura en el terreno de la eficiencia energética, pero que además más allá de la litografía esta arquitectura Zen 4 trae un 14 % más de instrucciones por ciclo ejecutada. Ese CCX, de ocho núcleos con 1 MB de caché de nivel 2 cada uno y 32 MB de caché de nivel 3 compartida entre ellos, tiene un tamaño de 55 mm2 con 6500 millones de transistores, de los 66.3 mm2 que tiene la estructura del CCD.

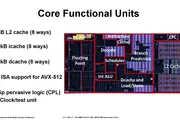

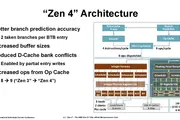

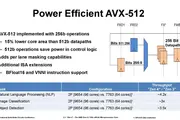

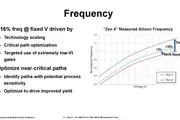

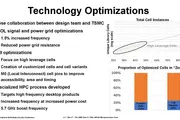

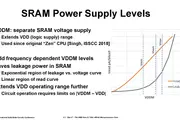

Muestra datos de los cambios a nivel de arquitectura en una de las trasparencias de su presentación del ISSCC, la cual la tenéis al final del artículo. Son cambios bastante relevantes, sobre todo a nivel del predictor de saltos (ejecución especulativa), carga/almacenamiento de datos y el frontal de ejecución. Como comentario adicional del proceso de 5 nm, hace uso de quince capas metálicas en lugar de las trece de los chips fabricados con el proceso de 7 nm. Son las encargadas de conectar los transistores, condensadores y otros elementos en los chips, por lo que da idea de una mayor complejidad de diseño.

En una de las trasparencias muestra que los chíplets Zen 4 están preparados para las vías a través de silicio que conectan con la V-Cache 3D de la compañía, por lo que lo han tenido ya en cuenta para reducir costes. También se ve el notable aumento de caché de nivel 2 que extiende el chíplet de V-Cache 3D con otros 64 MB de N2. Tiene un tamaño de 36 mm2 e incluye 4700 millones de transistores, estando fabricado a 7 nm lo que arroja 130.6 millones de transistores por milímetro cuadrado, una altísima densidad cortesía de que la estructura es solo de transistores y se conectan por vías a través de silicio al CCD.

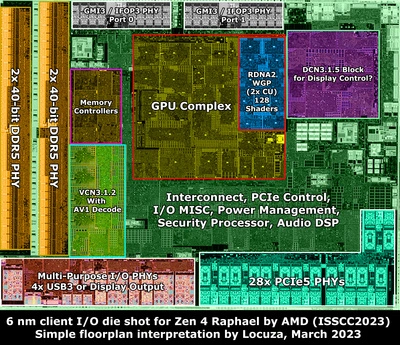

En base a la informción de las trasparencias y al diagrama del chíplet de E/S mostrado por AMD se puede desglosar los distintos componentes de su diseño. Eso incluyen los dos canales de control a nivel físico de la DDR5, la zona del controlador de memoria, el decoficador de vídeo, la iGPU de dos unidades de cómputo dobles (128 sombreadores), más los 28 canales PCIe 5.0 que tiene o la conectividad USB 3 y salidas de vídeo.

Vía: Tom's Hardware.