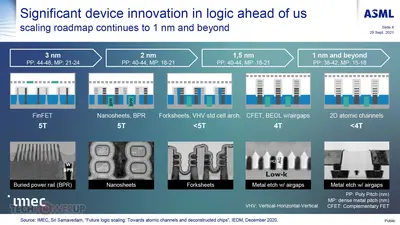

Intel está muy cerca de empezar a producir chips a 1.8 nm. Si todo va bien, a finales de 2024, un año del que ya estamos cerca. Por eso en el sector de los semiconductores se tiene puesta la mirada en las próximas formas de producir las estructuras de los transistores en las obleas con el objetivo de reducir su consumo y mejorar el rendimiento general de los chips lógicos. Actualmente estamos en los GAAFET o nanoláminas, pero habrá que dar un salto radical hacia los CFET. Intel y TSMC hablarán de sus progresos en la Conferencia Internacional de Dispositivos Electrónicos (IEDM) del 9 al 13 de diciembre.

Los transistores de efecto de campo complementario o CFET que pasan de tener las uniones PN de los transistores separadas horizontalmente a separarlas verticalmente. O sea, se apilan. Esto permitirá una mayor compactación de los transistores. Para producirlos se necesitará la maquinaría litográfica de alta apertura numérica (AN), que no entrará en servicio hasta el próximo año o el siguiente. Pero quizás no sirva la primera generación de alta AN, sino que habrá que esperar a la segunda.

TSMC ha comentado anteriormente que ya tiene a los CFET funcionando en el laboratorio, pero todavía falta llevarlos a producción real. TSMC habla de una separación entre puertas (uno de los terminales de los transistores) de 48 nm. Intel dará una charla similar a TSMC, pero siempre basándose en pruebas de laboratorio y no en pruebas de producción, y quedándose en una separación de 60 nm. Que en este caso es en vertical y no en horizontal.