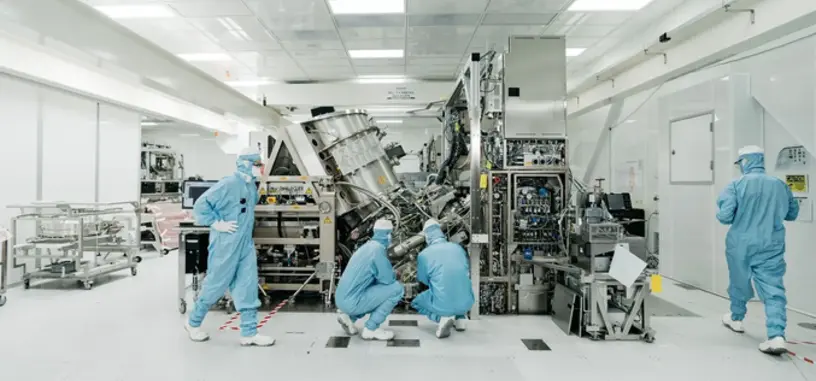

ASML ya está produciendo sus escáneres litográficos de alta apertura numérica (AN), de las cuales empezarán a salir chips comerciales el próximo año. Pero con su poder de investigación está explorando cómo habilitar que se siga reduciendo el tamaño de los transistores porque la alta AN tiene sus limitaciones. Eso pasará por la hiper-AN, que si la investigación de la compañía va bien, el primer escáner de hiper-AN estaría listo en torno a 2030.

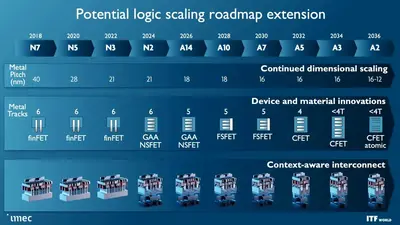

Si en alta AN la apertura numérica es de 0.55, en hiper-AN se pasaría a 0.7, lo cual permitiría concentrar más energía en menor espacio y así transferir mejor y más rápido los patrones de los fotolitos a las obleas. La idea es seguir con la reducción litográfica cada dos años, como también ha indicado el Imec (Centro Interuniversitario de Microelectrónica).

En torno a 2030 se bajará a los 0.7 nm, aunque no sería hasta 2032 y los 0.5 nm cuando se cambiaría a los CFET, que se basan en desdoblar los transistores en sus uniones P y N, y apilarlas en nFET y pFET. Se ahorra espacio y se mejora la entrega de energía. TSMC está ya investigando esta vía de transistores, pero su itinerario es similar al del Imec. Para estos es previsible que ya se necesitara la maquinaria de hiper-AN.

Vía: Tom's Hardware.