Intel está preparándose para poner en el mercado los procesadores Xeon 6 para los cuales va a usar su proceso litográfico de 3 nm al que llama simplemente «3», por alguna razón. En el simposio VLSI del IEEE que se está celebrando en Hawái, la compañía ha hablado del proceso litográfico y de los avances que está haciendo en el terreno de las litografías. De entrada ha asegurado que los 3 nm le permiten dar a sus chips hasta un 18 % más de rendimiento a mismo consumo que la litografía de 4 nm.

Con él también ha conseguido una reducción del área lógica de los chips en un 10 %. Asegura que es un proceso litográfico que está centrado en la computación de alto rendimiento, permitiendo producir chips con un voltaje bajo, inferior a los 0.65 V, pero también para alto voltaje, por encima de los 1.3 V. Eso le dará mucho juego para producir chips según el mercado específico al que vaya. Para cómputo, en unos predomina el número de núcleos frente a la frecuencia de funcionamiento, mientras que otros es al revés, menos núcleos pero a mayores frecuencias.

En la presentación, que está publicada en la web de Intel pero no he visto que esté el vídeo en YouTube, describe las distintas opciones de configuración del Intel 3, porque permite hacer chips más compactos con menos frecuencia máxima —cuanto más compacto es un chip más se concentra el calor, lo cual genera problemas adicionales como peor conducción eléctrica— o más dispersos pero con mayor frecuencia máxima. Es bastate configurable para Intel, y próximamente los clientes de Intel Foundry, que es por lo que ha hablado de esas posibles configuraciones de los transistores.

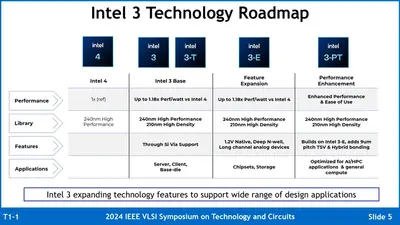

Dentro de la información proporcionada se encuentran las variaciones de este proceso 3 que serían las 3-T, 3-E y 3-PT, cada una con una mejora distinta relacionada con la forma de conectar las zonas lógicas con el exterior (3-E) a través de bibliotecas de componentes predefinidas por Intel, o con el diseño interno de los propios chips que permitan por ejemplo aplicarlos más fácilmente (3-T).