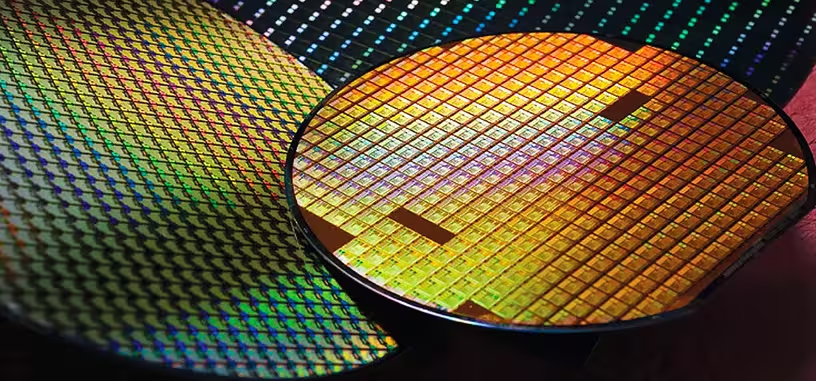

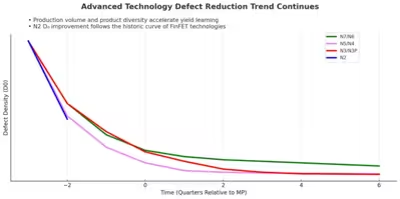

TSMC ha dado detalles esta semana de varios de sus procesos litográficos, y ha tenido tiempo para hablar del desarrollo de su litografía de 2 nm (N2). Es el primer proceso en el que usa los transistores de efecto de campo de puerta envolvente (GAAFET), lo cual va a proporcionar una mejora sustancial de rendimiento. Pero más allá de eso, de cara a sus clientes es más importante la tasa de defectos o densidad de defectos por oblea, de cual ha sido que en el N2 es menor que en el proceso de 3 nm (N3) en su punto actual de desarrollo.

El proceso llegará después del verano en dispositivos, en torno a septiembre u octubre en los procesadores de los iPhone 17, y a dos trimestres vista, la tasa de defectos es inferior a la que tuvo el N3 por un estrecho margen. En la práctica son buenas noticias porque el cambio de diseño de los transistores no parece que haya afectado a la producción de las obleas.

Es un cambio mayor por cómo hay que distribuir los tres terminales de un transistor, que en este caso es un canal común entre varios transistores con una puerta que lo envuelve totalmente. Con ese mayor control electrostático, el canal puede ser más o menos largo u ancho para aumentar o disminuir el paso de corriente, lo cual afecta al consumo o al rendimiento. En este caso TSMC lo ha desarrollado como nanoláminas configurables.

Vía: Tom's Hardware.