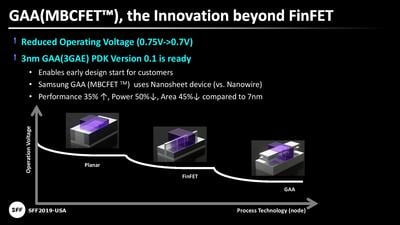

Samsung y TSMC están en un mano a mano a ver quién avanza más rápido en las tecnologías de procesos litográficos, y de momento Samsung está haciendo valer los miles de millones que se gasta anualmente en I+D+i. Por eso ahora ha hablado sobre su proceso de 3 nm, para el cual ya tiene una versión alfa para sus clientes del paquete de diseño de producto con el que pueden empezar a valorar sus futuros diseños de chips.

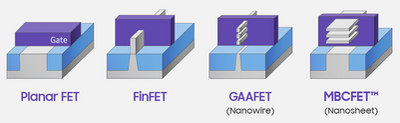

Lo más importante de este proceso de 3 nm es que Samsung va a hacer el cambio de los actuales FinFET (transistor de aleta de efecto de campo) a los transistores GAAFET (transistor de efecto de campo de puerta amplia, gate all-around). Los FinFET usan unas pequeñas y largas aletas para conectar la fuente y drenador a la puerta, que son los tres componentes básicos de los transistores de efecto de campo —en Hispanoamérica se les llama surtidor, drenador y compuerta—. Un transistor es una especie de interruptor que, dependiendo de cómo fluya la corriente, la deja pasar o no, activando o no los circuitos relacionados.

Los transistores de puerta amplia hacen que la puerta esté incrustada en el canal común para poder apilar los transistores verticalmente en lugar de ponerlos horizontalmente, con lo que se gana además en espacio pero obviamente es un proceso de fabricación aún más complejo. De ahí salen dos tipos de GAAFET, uno que usa nanocables para hacer de fuente y drenador, y la que propone Samsung de usar un canal más ancho con un drenador y fuente que son nanoplanchas (transistor de efecto de campo de canal multipuente, MBCFET), pero que en esencia es el mismo GAAFET con otra implementación física.

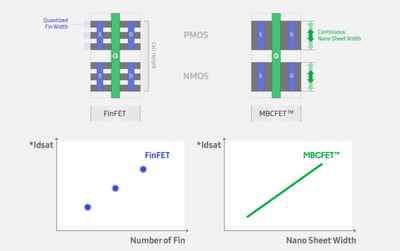

Este uso de los GAAFET/MBCFET llegará en los 3 nm como he dicho, y eso tendrá algunas ventajas adicionales según lo indicado por Samsung en el Foro de Fundiciones de Samsung 2019 celebrado en EE. UU. —fundición es como se llama en el sector específicamente a las fábricas que producen chips—. Lo indicado por Samsung a sus socios en esta primera versión de desarrollo de chips con MBCFET es que el ancho de las nanoplanchas es personalizable y determinan el rendimiento y consumo de los transistores.

Cuanto más anchas las nanoplanchas más rendimiento tendrá el chip pero también más consumo. Samsung les aporta cuatro diseños preestablecidos distintos de MBCFET para los primeros diseños, aunque el documento irá variando a medida que el proceso madure porque ahora mismo está en versión alfa y por tanto sujeto además a cambios.

Por tanto, ajustando el tamaño de esas nanoplanchas pueden crearse con este proceso ciertos chips de mucho menor consumo orientado a sectores como el internet de las cosas, o aumentar su tamaño para crear los habituales procesadores de sobremesa, o algo intermedio para procesadores de arquitectura ARM. En lugar de puntos concretos de potencia-rendimiento como ocurre en los FinFET, los MBCFET ofrecen infinidad de posibilidades a gusto del cliente.

Esta primera versión de los MBCFET funcionan a un voltaje algo inferior de 0.70 V, y en comparación con los 7 nm de la compañía lo que se ganaría con este proceso de 3 nm sería un 35 % más de rendimiento, la reducción del consumo a la mitad, y la reducción del área un 35 %.

Y además Samsung mantiene un itinerario bastante agresivo con este proceso, por lo que parece que las compañías han solucionado antes de los previsto los problemas con los procesos de fabricación por debajo de los 7 nm. Samsung espera empezar a hacer pruebas de producción de diseños de sus clientes en 2020 para la primera generación (3GAE), empezar la producción de riesgo a finales de 2020, y dar comienzo a la producción en masa en 2021. La segunda generación (3GAP) esperan hacer la producción de riesgo en 2021 y producción en masa en 2022.

Vía: AnandTech.