Rambus es una de las principales empresas dedicadas a interconexiones a nivel físico de los protocolos de comunicaciones, ya sea el de la RAM o, como es el caso que me ocupa, de conexiones PCIe. La compañía ha anunciado que tiene disponible para licenciar la conexión a nivel físico (PHY) de PCIe 6.0, la cual es una conexión que las compañías del sector de los centros de datos han estado acelerando para resolver las limitaciones de transmisión dentro de los propios centros de datos.

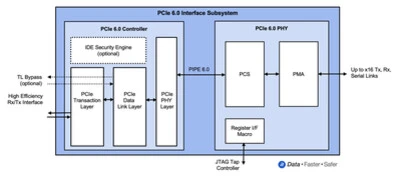

Esta conexión es compatible con el enlace de cómputo exprés (CXL) en su tercera versión, cuyo desarrollo está liderado por Intel aunque todas las compañías del sector se han ido sumando poco a poco, como AMD. Lo desarrollado es específicamente el subsistema de interfaz a añadir a chips que implementen PCIe 6.0, asegurando que se alcanzan los 64 Gb/s dúplex por canal. En esta especificación se pasa a un código de línea PAM4, que no es para nada avanzado pero que hace el apaño para asegurar el aumento de velocidad. También dispone de corrección de errores hacia delante (FEC) de baja latencia, una codificación redundante de la información a enviar a nivel físico para detectar errores.

La entrada de la comunicación a este subsistema encargado de enviar las señales a nivel físico —o sea, mediante voltajes— es la extensión a medio físico (PMA), que son los pines de conexión, y una subcapa de código físico (PCS) configurable. A partir de ahí se hace la comunicación con el controlador de la conexión PCIe para que el conjunto pueda ser retrocompatible con las especificaciones anteriores. Una conexión PCIe 6.0 ×16 permitirá hasta 128 GB/s bidireccionales de transferencia. La versión PCIe 7.0 está en desarrollo y se espera que esté lista para algún momento de 2024 o 2025.

Vía: TechPowerUp.