Los principales productores de semiconductores saben perfectamente que la ley de Moore ha obligado a la reducción del tamaño de los transistores topándose con escollos en el proceso como es el tamaño de los propios chips. Para avanzar en esta ley lo que empresas como Intel y TSMC han desarrollado es, tomando buena nota de los productores de memoria, tecnologías de apilamiento de chips usando vías a través del silicio para unir distintos chips. Samsung es la siguiente en sumarse a estas tecnologías.

En esta caso no me refiero al mero apilamiento de chips de mismo tipo, que sería sencillo como ocurre con la DRAM o la NAND —chips de memoria principal de un sistema y la memoria flash usada en las unidades de estado sólido—, sino chips de distinta índole. Intel tiene la tecnología Foveros y los procesadores Lakefield como muestra de ello, y está desarrollando otras tecnologías relacionadas con ese apilamiento para circunvalar la ley de Moore y permitir una mayor densidad de transistores por milímetro cuadrado usando una «tercera dimensión».

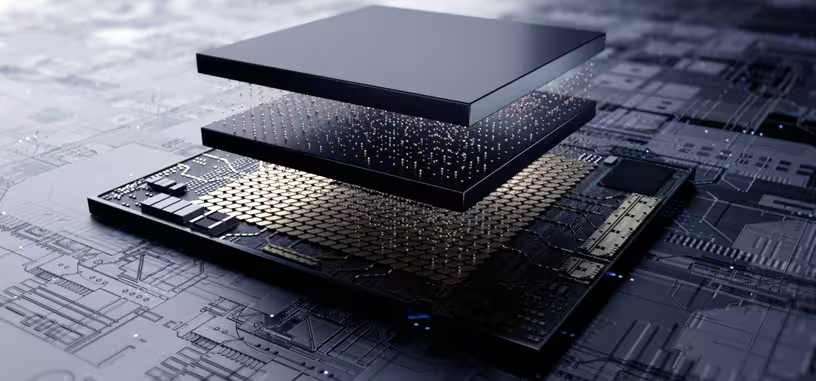

La nueva tecnología de Samsung se llama X-Cube, y permite interconectar directamente en el mismo encapsulado un chip de procesamiento con la memoria directamente ubicada encima. Hay diversas cuestiones de diseño que hay que tener en cuenta, sobre todo de tipo térmico y disposición de las interconexiones para la correcta fabricación de estos procesadores, pero para ello Samsung asegura haber creado toda la documentación y herramientas necesarias para entender cómo hacerlo y realizarlo de la mejor manera posible.

Puede que parezca una mención casual de Samsung, pero es que es lo que más se critica de Samsung Foundry: la falta de documentación y herramientas de sus procesos litográficos. Y aunque X-Cube no es una litografía sino un proceso de encapsulado, hay mucho recelo hacia Samsung Foundry. Si os preguntáis por qué no usan más diseñadores de chips a esta compañía para producirlos, en parte es por esa complejidad extra que históricamente ha tenido fabricación en las fundiciones de Samsung. Pero eso está cambiando para bien.

La integración vertical de chips mediante vías a través de silicio —sigla TSV por si lo veis en alguna parte, que no soy dado a usar siglas porque considero que las siglas ofuscan el mensaje salvo que esté muy asentada a nivel de que la entienda hasta mi abuela— permite integrar en el mismo encapsulado la memoria principal del sistema y al menos un chip de procesamiento. Al menos según lo mostrado por X-Cube, porque en ningún momento hace referencia a que puedan ser varios chips de distinta índole más la memoria. De momento hace referencia a apilar solo dos chips, uno de ellos fabricado a 7 nm debajo de un chip de memoria, pero sirve para chips fabricados a 5 nm.

Una ventaja inmediata de esta verticalidad es que se reducen las pistas de interconexión entre el chip y la memoria, lo que tiene un beneficio directo en la latencia de acceso a la memoria principal. También está la ventaja de que se aumenta el ancho de banda máximo debido a que se mantiene mejor la integridad de la señal de comunicación a altas frecuencias. En algunos casos es casi obligatorio que sea el menor recorrido posible como por ejemplo al usar memoria de alto ancho de banda (HBM) con una unidad de procesamiento gráfico. Por tanto, esto del apilamiento de chips es más una necesidad del sector que un extra opcional. Y por cierto, no solo las fundiciones investigan en esto. AMD tiene su encapsulado X3D en desarrollo y Apple lleva usando cosas similares para compactar procesadores como los del Watch. Esto también va más allá del mero soldado de la RAM al procesador que se hace actualmente en móviles porque son dos chips distintos y estas tecnologías lo que hacen es unir los chips en bruto o pastillas en el mismo encapsulado.