La fundición más avanzadas usada por terceros para producir sus diseños es indiscutiblemente TSMC. Puede que Samsung haya hecho progresos y abierto nuevas líneas de fabricación para esas empresas, pero todavía le falta limar asperezas a la hora de facilitar el diseño de los chips y los programas de pruebas. Sea como sea, ambas compañías llevan unas semanas hablando sobre sus procesos de 3 nm de manera superficial, si bien TSMC ha querido ahora seguir haciendo ruido con este proceso litográfico que no se usará en producción en masa hasta 2022.

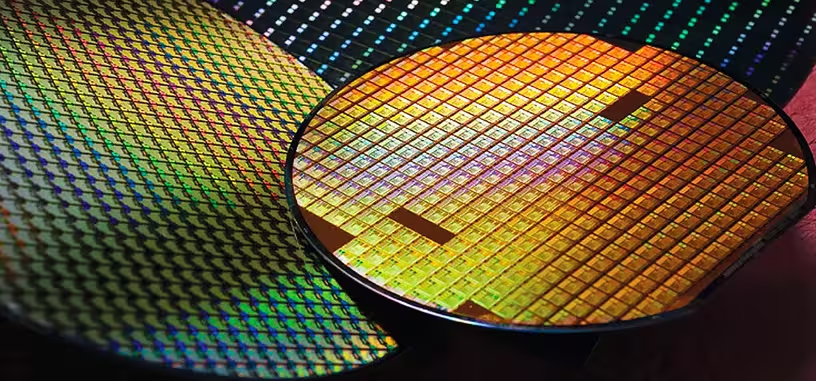

Lo hace además junto a la neerlandesa ASML, el principal fabricante de escáneres para producción de obleas, porque esos procesos litográficos de 3 nm de Samsung y TSMC no serían posibles sin sus escáneres de luz ultravioleta extrema (UVE). El nodo de 3 nm —«N3» en nomenclatura de TSMC— será completamente nuevo por lo que no será una mera evolución del de 5 nm UVE, proporcionando hasta un 15 % más de rendimiento a mismo consumo y cantidad de transistores, reducirá el consumo hasta un 30 % a misma frecuencia y complejidad, y aumentará la densidad de transistores en hasta un 70 %.

ASML ha indicado el proceso N3 de TSMC usará luz UVE en más de una veintena de capas. El uso de luz UVE implica que se simplifica el diseño de los chips al prescindir de la creación de cada capa con patrones múltiples, que actualmente suelen ser unos cuatro patrones. Léase «pasos» en lugar de patrones, por lo que de necesitar una capa de cuatro pasos para crearla se pasa a necesitar solo uno. Eso implica una reducción del tiempo de fabricación de la oblea, lo que se traduce también en un menor coste de producción, a pesar de que al ser un nodo puntero sea de por sí bastante más caro.

Actualmente el proceso N5 usa luz UVE en unas diez capas según el diseño. El uso de patrones múltiples se mantiene en estructuras complejas dentro de los chips y más sensibles como por ejemplo las partes de cachés o DRAM, pero en ASML creen que sus escáneres y la tecnología de TSMC permite usarla incluso con la DRAM. Este comentario del director ejecutivo de ASML está claramente orientado a que otros fabricantes de DRAM como SK Hynix, Samsung o Micron tomen nota.

Como se ha comentado anteriormente, el punto gris de TSMC es que seguirá usando la estructura FinFET (transistor de efecto de campo de aleta) y solo en el paso al proceso de 2 nm (N2) se hará uso de una estructura GAAFET (transistor de efecto de campo de puerta completa) que es necesaria para controlar las pérdidas y mejorar la eficiencia de los chips fabricados en ese nodo N2.

Vía: Tom's Hardware.