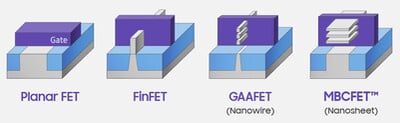

Aunque todavía pilla un poco lejos y apenas ha echado a rodar el proceso litográfico de 5 nm, el de 2 nm de TSMC sigue su desarrollo viento en popa. Tan bien está marchando que se está diciendo que la compañía ha conseguido un gran avance en el desarrollo de este proceso litográfico como para mantener vivas las esperanzas de que podrán comenzar las producciones de pruebas en algún momento de 2023. Por ahora el proceso de 3 nm, basado todavía en los transistores de efecto de campo de aleta (FinFET), sigue su desarrollo para entrar en producción de prueba en 2021 y producción en masa en 2022. De qué se trate ese gran avance no se especifica, pero siempre está bien hablar del futuro de los semiconductores.

TSMC, al menos según la rumorología, va a recurrir a los GAAFET en el proceso litográfico de 2 nm, por lo que no solo se enfrenta a los problemas de reducir algunos de los parámetros de los transistores sino que también se enfrenta a la creación de estructuras totalmente nuevas. GAAFET es la sigla de 'transistor de efecto de campo de puerta completa', un tipo de transistor en el que su fuente y drenador pasan a ser un nanotubo, por lo que están completamente rodeados por la puerta, y apilado con otros para tener una forma adicional de controlar las fugas de corriente según su tamaño y además poder así ahorrar espacio.

Samsung va a usar nanoplanchas en lugar de nanotubos en su tecnología propietaria MBCFET™ en su proceso de 3 nm. Por eso me hace gracia que en todas partes digan que TSMC usará MBCFET™, lo cual es imposible.

Vía: TechPowerUp.