SK Hynix ha anunciado un nuevo avance en la densidad de bits por milímetro cuadrado en su memoria NAND con el anuncio de los primeros chips NAND 4D de 176 capas. Tienen una capacidad de 512 Gb (64 GB) y son de tipo TCL (tres bits por celda), por lo que se podrán crear unidades de estado sólido de mayor capacidad en el mismo espacio como las de tipo M.2. De hecho la compañía habla de que aumenta un 35 % la cantidad de bits por oblea respecto a la generación anterior, lo que reduce los costes.

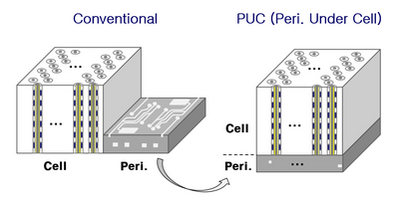

La tecnología NAND 4D de SK Hynix recibe su nombre porque frente a la NAND 3D tiene la circuitería periférica debajo de la celda (PUC) en lugar de al lado, lo que permite aprovechar más el espacio en la oblea pero aumenta la complejidad de producción. Esto tiene un efecto directo en el conexionado entre la lógica de la memoria y el almacenamiento de los bits, permitiendo un aumento de la velocidad de lectura de las celdas en un 20 %, mientras que la velocidad de transferencia de los chips se mejora hasta un 33 % hasta los 1.6 Gb/s por pin.

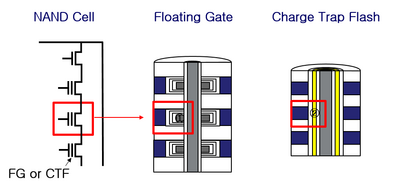

La compañía también hace uso de memoria de trampa de carga con un dieléctrico de alta permitividad relativa —anteriormente constante dieléctrica—, obteniendo mejoras en la velocidad de programar la celda, borrarla, elimina interferencias entre celdas y supone menos fugas, y también reduce el área de las celdas.

Otro aspecto que ataca el proceso de fabricación diseñado por SK Hynix es el grosor de las capas. Al aumentar su número es más difícil realizar las vías de conexión vertical y pueden suponer pérdidas de corriente y aumentar la resistencia. Al reducir el grosor de las capas se aumenta la tasa de defectos y la interferencia entre celdas. Con el nuevo método de SK Hynix se consigue una buena relación entre rendimiento y fiabilidad durante el proceso de fabricación.

Vía: Guru3D.