Ha habido muchas exageraciones y medias verdades sobre supuestos problemas con el proceso de 5 nm de Samsung, pero la compañía quiere resarcirse de todas ellas con el proceso de 3 nm. Es un cambio importante en la forma de fabricar los transistores por lo que hay mucha expectación sobre su potencial real. Ahora la compañía ha confirmado que iniciará la producción en masa con este nodo litográfico durante este segundo trimestre del año.

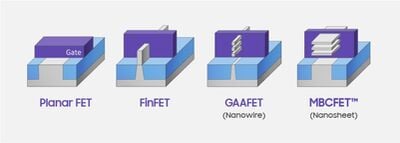

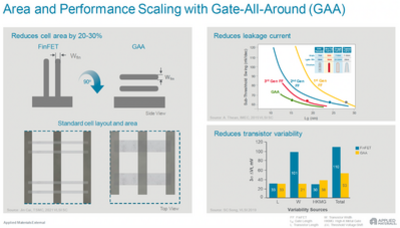

Samsung usa los MBCFET, el nombre específico que le da la compañía a los GAAFET o transistores de efecto de campo de puerta amplia en los que los canales se apilan y son rodeados por el material que hace de puerta, uno de los tres terminales de los transistores. La particularidad de MBCFET es que usa nanoláminas como canal en lugar de nanotubos, pero la tecnología subyacente es la misma. Esas nanoláminas son de ancho personalizable para el diseño específico de chip de cada cliente.

Esta estructura permite un ajuste más granular de la energía, con menos pérdidas. Según los datos proporcionados por la compañía, frente al proceso de 7 nm se reduce a la mitad el consumo a misma frecuencia o se aumenta el rendimiento un 30 % a mismo consumo, y se reduce un 45 % lo que ocupan los transistores.

El proceso tiene la denominación 3GAE (3 nm GAAFET preliminar), y por ello será usado principalmente por la propia Samsung a través de Samsung LSI, y probablemente por un par de clientes importantes de Samsung Foundry siempre que la productividad del proceso de fabricación sea el adecuado.

Vía: Tom's Hardware.