TSMC pondrá en producción a finales de año su proceso litográfico de 3 nm, y el siguiente salto será a los 2 nm. En este último hay un cambio en la forma en que se crean los transistores, de los FinFET a los GAAFET, lo cual le ha llevado bastante tiempo de investigación a la compañía. Pero una vez hecho el cambio, se espera que la siguiente litografía sea un poco más fácil de desarrollar. Esa será la de 1.4 nm, a la que TSMC pasará en junio su personal de I+D desde el proyecto de 3 nm.

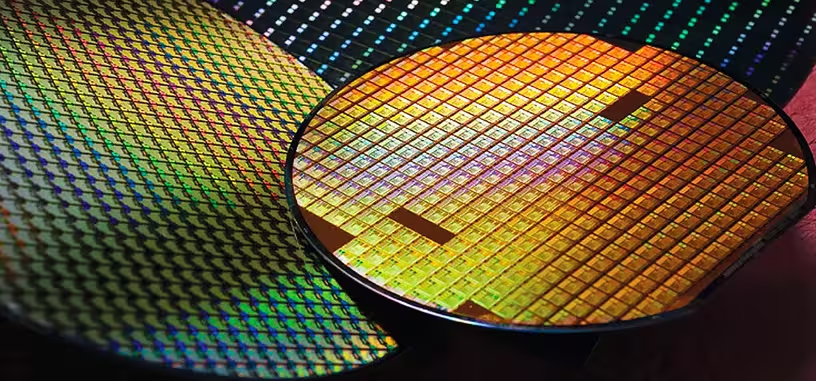

El proceso de 2 nm entrará en producción en 2025-2026, por lo que el de 1.4 nm tendría que ser en torno a 2027-2028. El equipo tendrá que buscar formas de plasmarlos en las obleas a estas litografías. TSMC no ha dicho si usará maquinaria ultravioleta extrema de alta apertura numérica en el proceso de 2 nm, pero en el de 1.4 nm casi se daría por hecho que la va a necesitar.

No está claro cómo van a conseguir las empresas reducir el tamaño de los transistores aunque hay diversas opciones que se han desarrollado a nivel universitario en los últimos dos o tres años. Esa es la parte fácil, porque la parte difícil es transferir esos patrones a las obleas en un proceso complejo de múltiples capas y decenas o cientos de etapas intermedias.

Vía: Tom's Hardware.