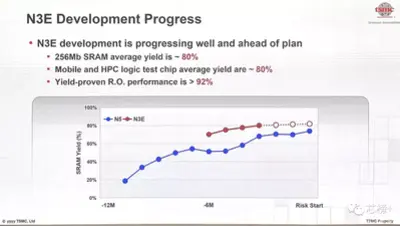

TSMC ha asegurado en los últimos tiempos que la velocidad de desarrollo del nodo de 3 nm ha ido bastante mejor que el de 5 nm. Los tiempos se han reducido y eso le ha permitido a la compañía redirigir personal a los procesos litográficos más avanzados. Una vez lleguen los primeros dispositivos con chips a 3 nm (N3) este mismo año, el siguiente proceso es el N3E, un «3 nm mejorado» del que aparentemente también lleva bastante más adelantado su desarrollo y, lo más importante, en su productividad.

Al menos según una supuesta trasparencia de la compañía, aunque encaja con lo dicho por TSMC anteriormente. Si la trasparencia no fuera cierta, al menos la información dada no es descabellada. Según esta, andaría ya por encima del 80 % de productividad —acepción tres del DLE; no digáis yield, por favor—. En el proceso N5 la compañía estaba en este punto por debajo del 70 %, el cual entró en producción de riesgo por debajo del 80 %. Sin embargo, TSMC meterá al N3E en producción de riesgo por encima del 80 %, según el tipo de chip que sea.

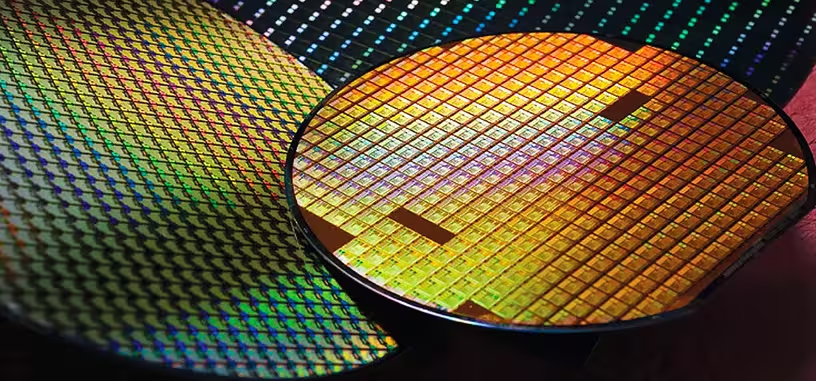

La productividad en este terreno es el número de chips válidos que se extraen de cada oblea. Lo que necesita conseguir TSMC es la mayor productividad posible para que realmente sea un proceso litográfico que le reporte beneficios desde el primer momento. Cuando la productividad es muy baja se tienen que vender las obleas a un precio bajo, o directamente retrasar el proceso litográfico hasta que se consiga un porcentaje mayor.

El proceso N3E llegaría en torno al tercer trimestre de 2023, y al menos estos datos son válidos para que a principios de 2023 entre en producción de prueba (o riesgo). Con lo que ha jugado TSMC en este nodo es que sigue usando los FinFET, por lo que realmente solo tenía que estar pendiente de la reducción de tamaño de los elementos de los transistores. O sea, una iteración más del proceso de 5 nm. En el proceso de 2 nm cambiará la estructura a los GAAFET, por lo que la información de ese proceso es la realmente relevante.

Vía: Tom's Hardware.