Intel avanzó hace unas semanas la llegada de una nueva familia de procesadores Xeon denominada Skylake SP. Tienen una nueva nomenclatura, y se dividen en los Xeon Bronce, Plata, Oro y Platino, con ciertas características compartidas con los chips de aceleración de computación Knights Landing, como QuickAssist y el conjunto de instrucciones de 512 bit llamado AVX-512.

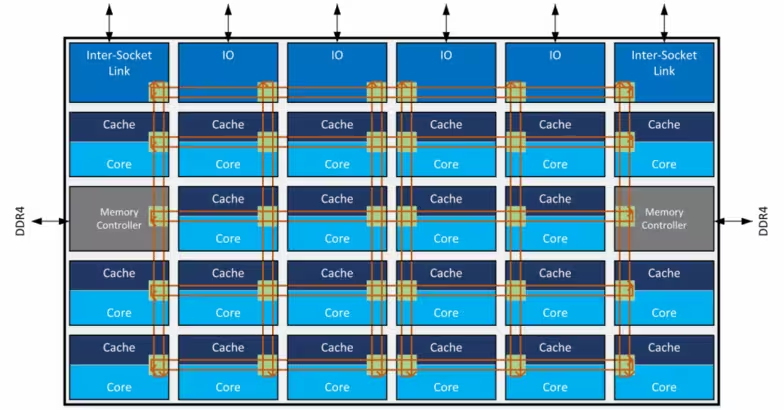

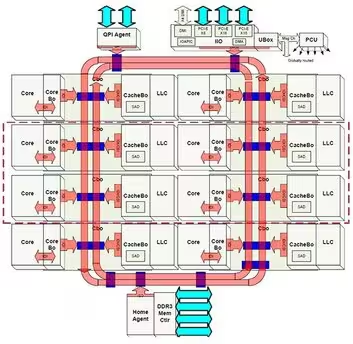

Este chip requiere de una nueva interconexión más eficiente y, sobre todo, que conecte a todos los núcleos con todos los demás núcleos. Es una interconexión en malla, más habitual en redes de computadoras y no tanto —por no decir nada habitual— en procesadores. La topología la tenéis a continuación, en un gráfico en el que Intel explica bastante bien en qué consiste.

El aspecto de estos chips es de un formato de array, con cada celda del array ocupada por un núcleo, controlador de memoria, controlador de E/S o interconexión del zócalo. Todas las celdas están conectadas con el resto al incluir el conexionado y conmutadores para enrutar la información y que termine en la celda oportuna, por lo que es una topología de red aplicada a un procesador.

Los procesadores usan normalmente una arquitectura de acceso a un bus de datos en anillo común que conecta a todos los componentes, y por el que en caso de congestión tienen que pelear por ganar acceso a él. Con esta topología, al estar distribuida la caché y resto de elementos también a lo largo y ancho del chip, se eliminan los puntos negros que puedan llevar a problemas de limitación por un uso intensivo de ciertos recursos, e Intel promete reducciones en el consumo.

Esta nueva interconexiónes de baja latencia, y que además tiene beneficios en aplicaciones de bases de datos, simulaciones de físicas complejas, aplicaciones intensivas de red y otros. Por último, con esta disposición, es más fácil coordinar el uso de núcleos de distintos procesadores en una misma placa base.

Vía: Hot Hardware.