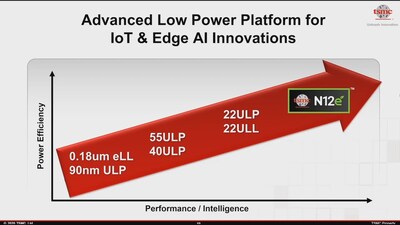

No todos los dispositivos necesitan los procesos tecnológicos más punteros y por eso en la actualidad se siguen utilizando mucho algunos procesos litográficos de más de 40 nm. Pero dentro de lo que cabe, todo tiene que evolucionar, y poniendo la mirada en el sector del internet de las cosas y la inteligencia artificial hay margen para mejorar el actual proceso 22ULP y 22ULL que ofrece TSMC a las compañías. El proceso tiene ventajas de un muy bajo consumo, idóneo para el internet de las cosas, pero la compañía ha desarrollado uno mejor y más específico de 12 nm denominado N12e.

La compañía parte del proceso de 16 nm FinFET que empezó a usar en 2013 y algunas partes de la tecnología 22ULL (ultra-low leakage, fuga ultrabaja) de 2018 y la 22ULP (ultra-low power, consumo ultrabajo), que son a su vez una evolución de los 40ULP y 50ULP. También aprovecha el 12FFC+ (FinFET compacto) para crear este N12e que recibe de muchas fuentes para proporcionar grandes mejoras en todos los terrenos.

TSMC habla, frente al 22ULL, de un 76 % más de densidad de transistores, un 49 % más de velocidad a mismo consumo, un 55 % de reducción de consumo a misma velocidad, reduce en más de un 50 % la corriente de fuga de la SRAM, y es compatible con bajos voltajes de operación, siendo de hasta 0.4 V. El apartado de la corriente de fuga es fundamental porque los chips para el internet de la cosa e inteligencia artificial integran por lo general su propia SRAM. Este proceso ofrece tecnología altamente estable para la memoria, con parámetros de consumo y funcionamiento bajos, y de bajo coste.

Vía: Guru3D.