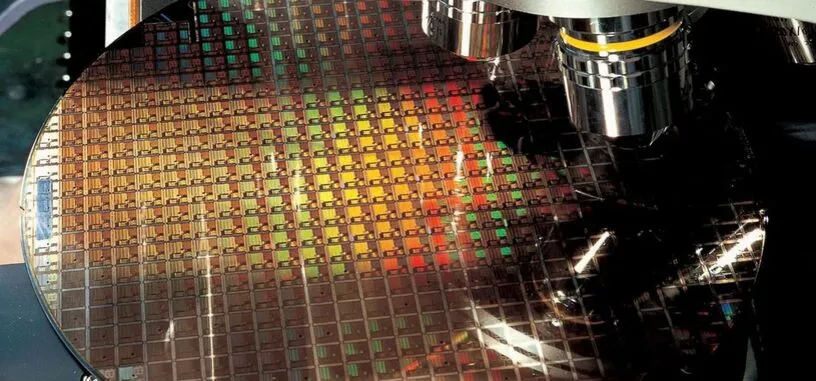

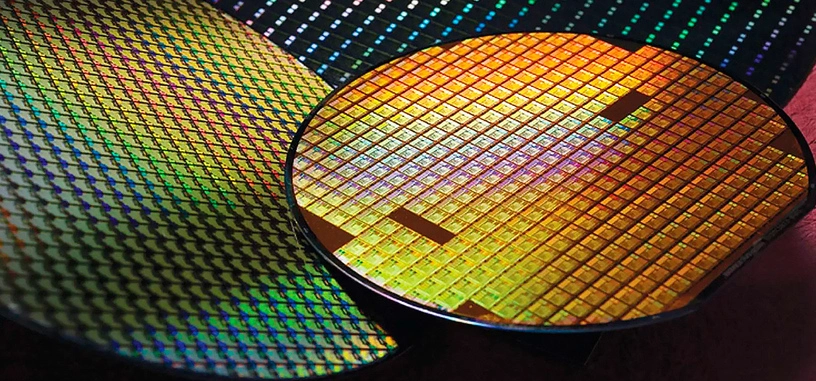

TSMC retrasa su fábrica de Arizona porque no encuentra estadounidenses cualificados

TSMC nunca ha tenido muchas ganas de abrir una fábrica de chips en EUA debido a que los costes iban a ser demasiado altos y los beneficios económicos nulos. Pero se decidió a abrir una por presiones geopolíticas y por las subvenciones prometidas por el estado de Arizona y por el Gobierno federal de los EUA, con Biden a la cabeza. Pero a la hora de la verdad, la compañía no ha tenido más que problemas a la hora de desarrollar el proyecto, y ahora ha aplazado la entrada en funcionamiento de la planta hasta (al menos) 2025.

Sigue leyendo