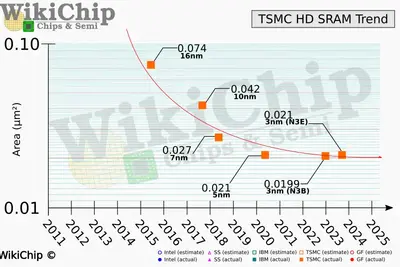

Uno de los problemas a los que se ha enfrentado TSMC en los últimos años en el desarrollo de sus litografías es el de la reducción de tamaño de la SRAM. Prácticamente no ha evolucionado desde 2020, lo cual es un problema para reducir el tamaño de los chips lógicos, principalmente las CPU y GPU, porque la SRAM es lo que es la memoria caché que incluye y ocupan un gran espacio de sus núcleos. Pero TSMC ha indicado que en su proceso de 2 nm ha hecho un gran avance en este terreno, lo cual son muy buenas noticias.

Este proceso litográfico será el primero de la compañía en usar los GAAFET, con ventajas en todos los frentes. TSMC dice que, frente a la litografía N3E, el proceso N2 aporta una reducción de consumo del 25-30 % a misma frecuencia, un 10-15 % más de rendimiento a mismo consumo, y un 15 % más de densidad de transistores a misma frecuencia y consumo. Luego en cada diseño de chip habrá que jugar con esos parámetros.

El apartado importante es que la compañía reduce el tamaño de las celdas de SRAM alta densidad (HD-SRAM) hasta los 0.0175 µm2, lo cual es un 14 % menos. Teniendo en cuenta que se había mantenido con una densidad similar desde el proceso de 5 nm de 2020, cualquier mejora en este apartado es bienvenida.

Vía: Tom's Hardware.